DC ANALYSIS OF p-n-p-n TUNNELING FIELD-EFFECT TRANSISTOR BASED ON In0.35Ga0.65As

DOI:

https://doi.org/10.15628/holos.2018.6173Palavras-chave:

Analytical model, semiconductor materials, Tunneling field-effect transistor, ON current, OFF currentResumo

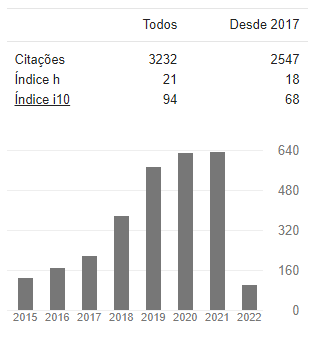

Using calibrated simulations, we report the In0.35Ga0.65As based tunnel field-effect transistor (TFET) with thin ?-doped n+ pocket at the source-channel interface to improve the parameters such as on current (Ion), off-current (Ioff) and subthreshold swing (SS). The simulations results of proposed device is compared with analytical model that is shown with high precision of DC parameters by examining the effects of III-V semiconductor materials. Furthermore, the influence of pocket doping, pocket width, doping level, effective oxide thickness (EOT), temperature and mole fraction of III-V semiconductor material on device performance have been investigated. The results show that proposed device has a higher ON current (1×10-5 A/µm) and a steeper subthreshold swing (35 mV/decade) as compared with the conventional TFET. It shows a lot of promise for future scale CMOS technology for low voltage and high frequency applicationDownloads

Referências

Atlas, D. S. (2010). Atlas User's Manual Silvaco Int. Software. Santa Clara. CA.

Bi, Y., Shamsi, K., Yuan, J. S., Jin, Y., Niemier, M., & Hu, X. S. (2017). Tunnel FET current mode logic for dpa-resilient circuit designs. IEEE Transactions on Emerging Topics in Computing, 5(3), 340-352.

Boucart, K., & Ionescu, A. M. (2007). Double-gate Tunnel FET With High K Gate Dielectric. IEEE Transactions on Electron Devices, 54(7), 1725-1733.

Brouzet, V., Salem, B., Periwal, P., Rosaz, G., Baron, T., Bassani, F.. & Ghibaudo, G. (2015). Fabrication and characterization of silicon nanowire pin MOS gated diode for use as p-type tunnel FET. Applied Physics A, 121(3), 1285-1290.

Chang, H. Y., Adams, B., Chien, P. Y., Li, J., & Woo, J. C. (2013). Improved subthreshold and output characteristics of source-pocket Si tunnel FET by the application of laser annealing. IEEE Transactions on Electron Devices, 60(1), 92-96.

Ganapathi, K., & Salahuddin, S. (2011). Heterojunction vertical band-to-band tunneling transistors for steep subthreshold swing and high on current. IEEE Electron Device Letters, 32(5), 689-691.

Gholizadeh, M., & Hosseini, S. E. (2014). A 2-D analytical model for double-gate tunnel FETs. IEEE Transactions on Electron Devices, 61(5), 1494-1500.

Guo, A., Matheu, P., & Liu, T. J. K. (2011). SOI TFET ION/IOFF Enhancement via Back Biasing. IEEE Transactions on Electron Devices, 58(10), 3283-3285.

Hosseini, S. E., & Moghaddam, M. K. (2015). Analytical modeling of a pnin tunneling field effect transistor. Materials Science in Semiconductor Processing, 30, 56-61.

Ionescu, A. M., & Riel, H. (2011). Tunnel field-effect transistors as energy-efficient electronic switches. nature, 479(7373), 329.

Jhaveri, R., Nagavarapu, V., & Woo, J. C. (2011). Effect of pocket doping and annealing schemes on the source-pocket tunnel field-effect transistor. IEEE Transactions on Electron Devices, 58(1), 80-86.

Kao, K. H., Verhulst, A. S., Vandenberghe, W. G., & De Meyer, K. (2013). Counterdoped pocket thickness optimization of gate-on-source-only tunnel FETs. IEEE Transactions on Electron Devices, 60(1), 6-12.

Khayer, M. A., & Lake, R. K. (2009). Drive currents and leakage currents in InSb and InAs nanowire and carbon nanotube band-to-band tunneling FETs. IEEE electron device letters, 30(12), 1257-1259.

Low, K. L., Yeo, Y. C., & Liang, G. (2016). Ultimate performance projection of ultrathin body transistor based on group IV, III-V, and 2-D-materials. IEEE Transactions on Electron Devices, 63(2), 773-780.

Marjani, S., & Hosseini, S. E. (2014). Radio-frequency modeling of square-shaped extended source tunneling field-effect transistors. Superlattices and Microstructures, 76, 297-314.

Marjani, S., & Hosseini, S. E. (2014, December). RF modeling of pnpn double-gate tunneling field-effect transistors. In Millimeter-Wave and Terahertz Technologies (MMWATT), 2014 Third Conference on (pp. 1-4). IEEE.

Marjani, S., & Hosseini, S. E. (2014). A novel double gate tunnel field effect transistor with 9 mV/dec average subthreshold slope. In the 22st Iranian Conference on Electrical Engineering (ICEE), 2014, (pp. 399–402),. IEEE.

Marjani, S., & Hosseini, S. E. (2015). Radio-frequency small-signal model of hetero-gate-dielectric pnpn tunneling field-effect transistor including charge conservation capacitance and substrate parameters. Journal of Applied Physics, 118(9), 095708.

Marjani, S., Hosseini, S. E., & Faez, R. (2016). A 3D analytical modeling of tri-gate tunneling field-effect transistors. Journal of Computational Electronics, 15(3), 820-830.

Marjani, S., & Hosseini, S. E. (2015, May). Analysis of radio frequency and stability performance on double-gate extended source tunneling field-effect transistors. In Electrical Engineering (ICEE), 2015 23rd Iranian Conference on (pp. 1042-1046). IEEE.

Marjani, S., Khosroabadi, S. and Hosseini, S. E. (2017). Enhanced characteristics of square-shaped extended source TFET via silicon carbide polytype (3C-SiC) and a dopant pocket layer. Orient. J. Chem., 33(3), 1083–1089.

Marjani, S., Hosseini, S. E., & Faez, R. (2016). A silicon doped hafnium oxide ferroelectric p–n–p–n SOI tunneling field–effect transistor with steep subthreshold slope and high switching state current ratio. AIP Advances, 6(9), 095010-1–095010-7.

Marjani, S., & Hosseini, S. E. (2015). Analyses on radio-frequency modeling of double-and single-gate square-shaped extended source TFETs. Journal of Electrical Systems and Signals, 3(1), 9–14.

Moore, G. E. (1965, January). MOS Transistor as an individual Device and in Integrated Arrays. In Ieee Spectrum (Vol. 2, No. 3, p. 49). 345 E 47TH ST, NEW YORK, NY 10017-2394: IEEE-INST ELECTRICAL ELECTRONICS ENGINEERS INC.

Narang, R., Saxena, M., Gupta, M., & Gupta, R. S. (2011, January). Modeling and simulation of multi layer gate dielectric double gate tunnel field-effect transistor (DG-TFET). In Students' Technology Symposium (TechSym), 2011 IEEE (pp. 281-285). IEEE.

Salehi, M. R., Abiri, E., Hosseini, S. E., & Dorostkar, B. (2013, May). Analysis and optimization of tunnel FET with band gap engineering. In Electrical Engineering (ICEE), 2013 21st Iranian Conference on (pp. 1-4). IEEE.

Vallett, A. L., Minassian, S., Kaszuba, P., Datta, S., Redwing, J. M., & Mayer, T. S. (2010). Fabrication and characterization of axially doped silicon nanowire tunnel field-effect transistors. Nano letters, 10(12), 4813-4818.

Wu, C., Huang, Q., Zhao, Y., Wang, J., Wang, Y., & Huang, R. (2016). A novel tunnel FET design with stacked source configuration for average subthreshold swing reduction. IEEE Transactions on Electron Devices, 63(12), 5072-5076.

Zhao, H., Chen, Y., Wang, Y., Zhou, F., Xue, F., & Lee, J. (2011). InGaAs tunneling field-effect-transistors with atomic-layer-deposited gate oxides. IEEE Transactions on Electron Devices, 58(9), 2990-2995.

Zhu, Y., Jain, N., Mohata, D. K., Datta, S., Lubyshev, D., Fastenau, J. M., ... & Hudait, M. K. (2013). Band offset determination of mixed As/Sb type-II staggered gap heterostructure for n-channel tunnel field effect transistor application. Journal of Applied Physics, 113(2), 024319.